ATI HD5xxx series.

-

http://www.laozaa.com/board/index.php?topic=6115.0

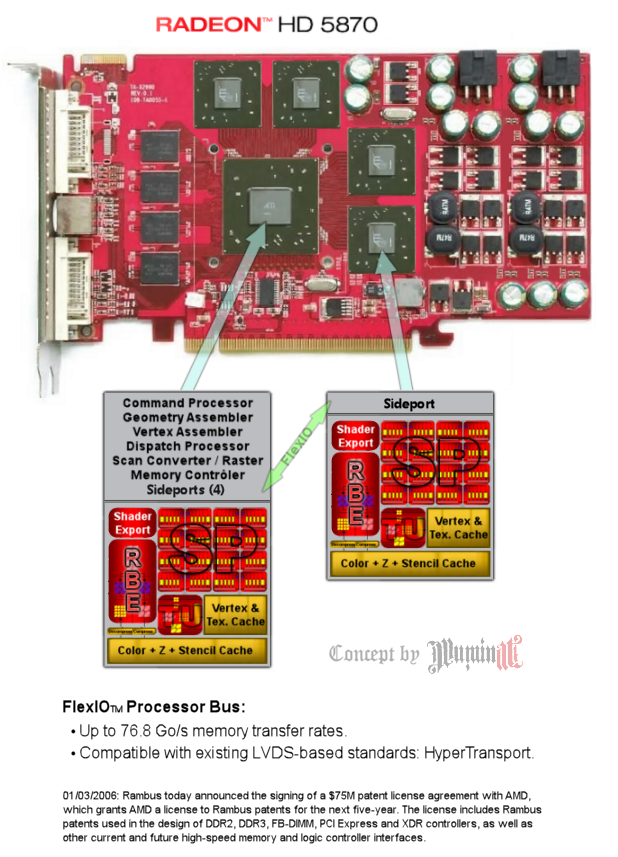

Aunke las imagenes parecen un fake lo interesante es su arquitectura, la cual estaria compuesta por chip maestro_- _-esclavo(s). Este ultimo vendria a ser una copia del maestro en lo referente a sp/tmus.

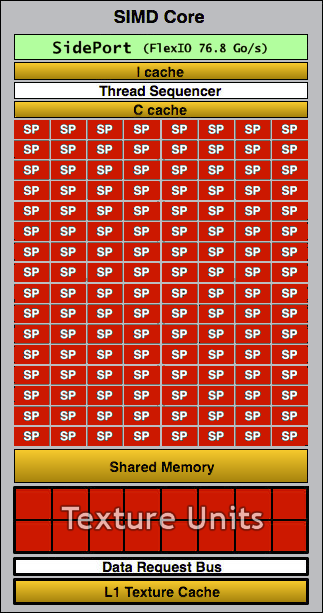

Estos chips esclavos estarian conectados al chip maestro mediante una interface de entrada y salida conocida como FlexIO constituida por 12 conexiones punto a punto unidireccionales de 1byte (5 de entrada y 7 de salida). Esta interface es rapidisima, pudiendo operar desde 400mhz hasta 8ghz de hecho es la que usa el chip cell (IBM) de la ps3, el ancho de banta teorico total se situa en 384 gb/s (4 x 76,8).

Se ve que las fotos son de hace varios años ya que se habla de ddr2 y ddr3, aunque tambien cita algo de XDR controller, si eso fuera cierto esta nueva serie podria utilizar memorias XDR de Rambus las cuales podrian llegar hasta los 6,33ghz (usadas ya por la ps3).

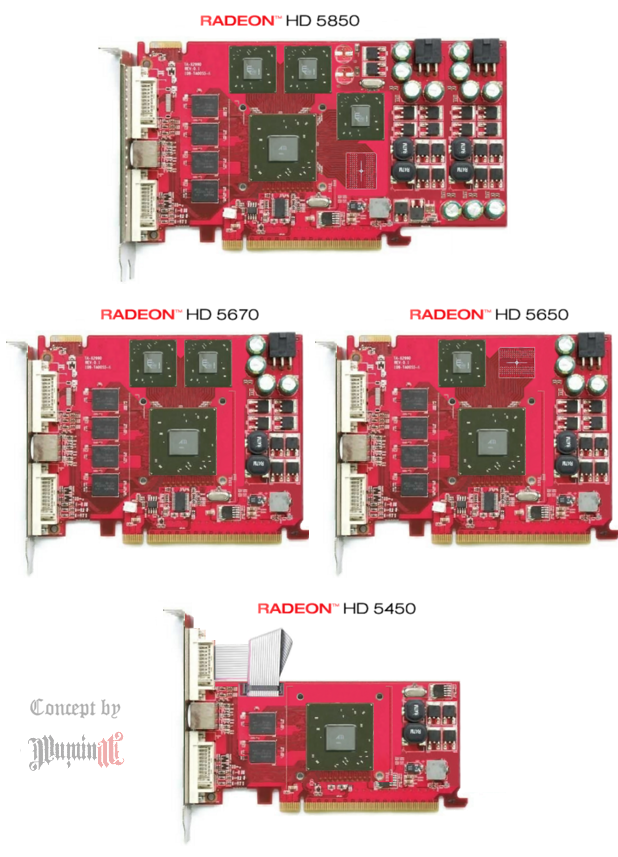

Otro factor interesante de esta arquitectura es que mediante el uso de los chips esclavo se reduce el tamaño del PCB, ya que para aumentar el rendimiento solo habria que poner mas chips esclavos y no usar 2 chips e interconectarlos con un chipset (como hasta ahora), con lo cual tambien se abarata el proceso.Traducción:

Pros:

- Se necesitan solo 2 chips (maestro/esclavo) para crear una serie completa de tarjetas gráficas.

- El chip esclavo es una copia exacta de la parte "SP/TMUs" del chip maestro. Por lo tanto, al crear un chip maestro, también estas creando el 95% del chip esclavo.

- Menos tiempo/diner necesitado para crear una nueva serie (9 meses en lugar de 12)

- Chips muy pequeños->Muy buenos Yields->muy buen precio.

- Arquitectura de memoria compartida.

Contras:

- Los más hambrientos de ancho de banda de memoria son los ROPs y las caches de textura L2, por lo que ATI a colocado físicamente estas unidades cercanas al controlador de memoria y ha utilizado miles de pistas para conectarlos. Por lo que por ahora es imposible colocar los RBEs al interior de los chips esclavos. Además, el chip maestro debe contener RBEs suficientes para la HD5870, pero este alto número de RBEs serán demasiados para las HD54XX/56XX. Este es quizá el mayor problema de diseño"

PD: "divide y venceras" xD

-

Hombre las imágenes ponen "concept", creo que queda claro que es.

-

Ya si esta claro k es concept, pk las imagenes son del 2006. Pero puede que la arquitectura si sea acertada y puede que no este tan alejada de la realidad.

-

a falta de algo más serio, lo dejamos en fake. si más adelante se confirma pues mejor