AMD "Bulldozer", 32nm - high-K - AM3… A finales de año con suerte.

-

"…

De todas maneras se hablá por ahí de la posibilidad de sacar un six-core bulldozer cosa que no termino de ver, por que en ese caso 2 de los "núcleos" perderían la capacidad de procesar flotantes en modo 256bits...¿Y eso por que?, según se aprecia cada uno de los núcleos tiene su propia unidad de coma flotante, es una unidad doble de 128bits cada una con un organizador que las maneja para los 8 threads físicos del núcleo permitiendo en cada ciclo instrucción de 128 o de 256bit según la necesidad, y esto es internamente e independientemente en cada nucleo, ya sea elcpu de 2, 4 6 u 8 núcleos (también habrá bulldozer de 8 cores).

Vamos que la posibilidad de procesar en cada ciclo instrucción fp de 128 o de 256bit según los hilos que soliciten fp dentro del núcleo, sera independiente entre núcleos, cada núcleo podrá gestionar independientemente su doble fpu de 128bit en cada ciclo de reloj.Es muy temprano la verdad para "pillarse los dedos" argumentando sobre esta arquitectura, en agosto se dice que habrá información algo mas fiable, pero si lo que se comenta es verdad este micro desbancara a intel a no se que esta misma tenga ya listo algo similar:

Fijaros que según la información disponible las imagenes que veis son de un core y no del cpu completo, esto supondría que estos micros tratarían instrucciones desglosadas pero de forma nativa o sea físicamente, y en ese caso este micro estaría por delante de cualquier i7 presente, y la tendencia es precisamente esa, cluster multi-hilo versátil capaz de usar los hilos independientemente o cumbinados según la necesidad de cada instrucción, o sea seria la siguiente devolución al hyperTrheding de intel.No me acuerdo donde he leído que Intel esta también trabajando con prototipos sobre esta misma arquitectura de cluster físico.

En cualquier caso mosquea bastante que en las imagenes este core (modulo como lo viene llamando amd) es etiquetado en conjunto como "bulldozer" lo que deja dudas

de si realmente es un núcleo o el micro completo o que es realmente. Y al mismo tiempo se puede apreciar que este "modulo" o núcleo integra también un modulo llamado "Shared L3 and NB",lo que me deja pensando si sera el micro completo o si sera una nueva manera de implementar el NB en la que cada núcleo se pudiera comunicar con el sistema independientemente, lo cual supongo que seria un gran avance.

de si realmente es un núcleo o el micro completo o que es realmente. Y al mismo tiempo se puede apreciar que este "modulo" o núcleo integra también un modulo llamado "Shared L3 and NB",lo que me deja pensando si sera el micro completo o si sera una nueva manera de implementar el NB en la que cada núcleo se pudiera comunicar con el sistema independientemente, lo cual supongo que seria un gran avance.Lo que si que esta claro es que la expectativa puede venir a ser muy fuerte !!! a ver si en agosto llega información mas fiable y así no tenemos que especular tanto

Salu2

-

¿Y eso por que?, según se aprecia cada uno de los núcleos tiene su propia unidad de coma flotante, es una unidad doble de 128bits cada una con un organizador que las maneja para los 8 threads físicos del núcleo permitiendo en cada ciclo instrucción de 128 o de 256bit según la necesidad, y esto es internamente e independientemente en cada nucleo, ya sea elcpu de 2, 4 6 u 8 núcleos (también habrá bulldozer de 8 cores).

Vamos que la posibilidad de procesar en cada ciclo instrucción fp de 128 o de 256bit según los hilos que soliciten fp dentro del núcleo, sera independiente entre núcleos, cada núcleo podrá gestionar independientemente su doble fpu de 128bit en cada ciclo de reloj.Es muy temprano la verdad para "pillarse los dedos" argumentando sobre esta arquitectura, en agosto se dice que habrá información algo mas fiable, pero si lo que se comenta es verdad este micro desbancara a intel a no se que esta misma tenga ya listo algo similar:

Fijaros que según la información disponible las imagenes que veis son de un core y no del cpu completo, esto supondría que estos micros tratarían instrucciones desglosadas pero de forma nativa o sea físicamente, y en ese caso este micro estaría por delante de cualquier i7 presente, y la tendencia es precisamente esa, cluster multi-hilo versátil capaz de usar los hilos independientemente o cumbinados según la necesidad de cada instrucción, o sea seria la siguiente devolución al hyperTrheding de intel.No me acuerdo donde he leído que Intel esta también trabajando con prototipos sobre esta misma arquitectura de cluster físico.

En cualquier caso mosquea bastante que en las imagenes este core (modulo como lo viene llamando amd) es etiquetado en conjunto como "bulldozer" lo que deja dudas

de si realmente es un núcleo o el micro completo o que es realmente. Y al mismo tiempo se puede apreciar que este "modulo" o núcleo integra también un modulo llamado "Shared L3 and NB",lo que me deja pensando si sera el micro completo o si sera una nueva manera de implementar el NB en la que cada núcleo se pudiera comunicar con el sistema independientemente, lo cual supongo que seria un gran avance.

de si realmente es un núcleo o el micro completo o que es realmente. Y al mismo tiempo se puede apreciar que este "modulo" o núcleo integra también un modulo llamado "Shared L3 and NB",lo que me deja pensando si sera el micro completo o si sera una nueva manera de implementar el NB en la que cada núcleo se pudiera comunicar con el sistema independientemente, lo cual supongo que seria un gran avance.Lo que si que esta claro es que la expectativa puede venir a ser muy fuerte !!! a ver si en agosto llega información mas fiable y así no tenemos que especular tanto

Salu2

Si que podría haber un bulldozer de 6 nucleos, llevas razón, sería un micro con 3 modulos, lo que no sería posible es un supuesto micro con 3 núcleos…

Lo que no entiendo muy bien es lo que dices de que cada núcleo puede gestionar su FPU doble. Por lo que se un modulo sería equivalente a 2 "núcleos" (dicho por AMD), por lo que habría una FPU doble en cada modulo. Eso querria decir que en un caso ideal que cargue el micro al 100% habría posibilidad de ejecutar en cada nucleo una unica instruccion FP 128 o ejecutar en cada modulo una unica instruccion FP256 (es decir, empleando 2 núcleos), por lo que la capacidad sería en un octo-core o bien de ejecutar 8 FP128bits simultaneos o 4 FP256 bits simultaneos (sin entrar a operaciones por ciclo y unidades de ejecucion de cada nucleo y demás).

Lo que si parece en un principio, viendo los 8 pipelines que tiene cada unidad de enteros en los modulos, que cada uno de ellos será visto por el SO como 8 hilos, haciendo un total de 32 hilos en un bulldozer zambezi de 8 núcleos, que es algo que se comentaba también tiempo atras...

-

Pues entonces ahy estara mi error; si en realidad cada modulo son dos cores la cosa cambia un poco la verdad.

Entonces sera como dices tu, cada modulo (o conjunto de dos cores) podria combinar sus dos unidades FP de 128 para ejecutar instrucciones FP de 256.Lo de tener integrado el bulldozer NB en cada modulo tambien me llama mucho la atencion, a ver como funciona eso en la practica.

Yo la verdad es que me he basado en las informaciones mas tempranas que he visto sobre el asunto. pero aun con tantas novedades interesantes, talvez lo que mas me llama la atencion es que los vayan a frabricar con material Hi-K, si salen por lo menos tan buenos como los Phenom II y encima con Hi-K seguro que consiguen un margen de overclock muy bueno, superior a los actuales (ojala), y si la politica de precios se mantiene es de suponer que seria un producto muy pero que muy interesante.

Salu2.

-

Pues entonces ahy estara mi error; si en realidad cada modulo son dos cores la cosa cambia un poco la verdad.

Entonces sera como dices tu, cada modulo (o conjunto de dos cores) podria combinar sus dos unidades FP de 128 para ejecutar instrucciones FP de 256.Lo de tener integrado el bulldozer NB en cada modulo tambien me llama mucho la atencion, a ver como funciona eso en la practica.

Yo la verdad es que me he basado en las informaciones mas tempranas que he visto sobre el asunto. pero aun con tantas novedades interesantes, talvez lo que mas me llama la atencion es que los vayan a frabricar con material Hi-K, si salen por lo menos tan buenos como los Phenom II y encima con Hi-K seguro que consiguen un margen de overclock muy bueno, superior a los actuales (ojala), y si la politica de precios se mantiene es de suponer que seria un producto muy pero que muy interesante.

Salu2.

Supongo que lo del NB integrado se referirá solo a integrar el controlador pcie dentro del micro, como los lynnfield de Intel, asi dejan las placas con solamente el southbridge, pero bueno, tendremos que esperar un mesecito para saber más…

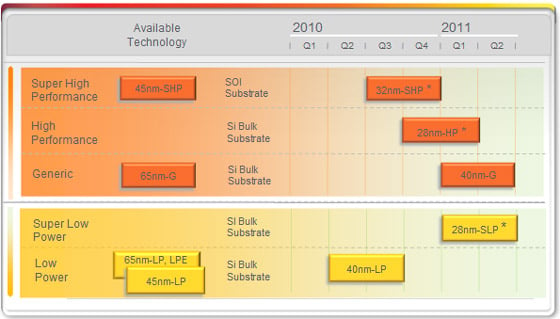

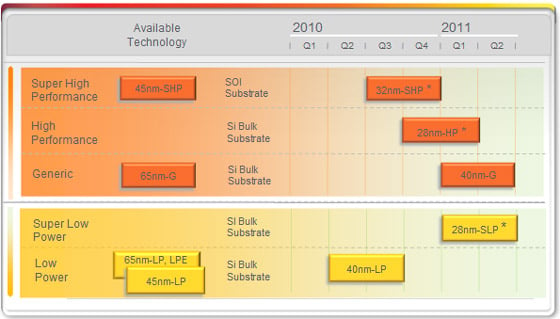

Por cierto, lo de los 32nm en High-K me parece que era un rumor solamente, por lo que se ve en los roadmaps de GlobalFoundries no tienen planes de pasarse a High-K y los 32nm seguirán siendo SOI:

Supuestamente el 32nm SPH es el orientado a las CPU, el 28nm HP el orientado a GPUs y el 28nm SLP el orientado a GPUs para portatiles.

Saludos

-

Supongo que lo del NB integrado se referirá solo a integrar el controlador pcie dentro del micro, como los lynnfield de Intel, asi dejan las placas con solamente el southbridge, pero bueno, tendremos que esperar un mesecito para saber más…

Por cierto, lo de los 32nm en High-K me parece que era un rumor solamente, por lo que se ve en los roadmaps de GlobalFoundries no tienen planes de pasarse a High-K y los 32nm seguirán siendo SOI:

Supuestamente el 32nm SPH es el orientado a las CPU, el 28nm HP el orientado a GPUs y el 28nm SLP el orientado a GPUs para portatiles.

Saludos

No si lo de NB integrado esta claro, todo tiene pinta que las arquitecturas disponibles van a imitar mas o menos a la distribucion que tiene ahora Intel en sus ix, pero lo curioso decia yo es el hecho de que cada "modulo" lleve su propio NB en lugar de haber un unico NB dentro del cpu.

Ya veremos como es todo finalmente, porque los rumores estan muy bien para crear espectativa pero de los rumores al resultado final a veces cambia tanto.

A ver dentro de un mesecito como pinta la cosa, a ver si progresan bastante o solo se renuevan un poco, por lo menos que pasen a 32nm verdad

Salu2.

-

No si lo de NB integrado esta claro, todo tiene pinta que las arquitecturas disponibles van a imitar mas o menos a la distribucion que tiene ahora Intel en sus ix, pero lo curioso decia yo es el hecho de que cada "modulo" lleve su propio NB en lugar de haber un unico NB dentro del cpu.

Ya veremos como es todo finalmente, porque los rumores estan muy bien para crear espectativa pero de los rumores al resultado final a veces cambia tanto.

A ver dentro de un mesecito como pinta la cosa, a ver si progresan bastante o solo se renuevan un poco, por lo menos que pasen a 32nm verdad

Salu2.

Hombre lo del NB en cada modulo igual es más cosa del dibujo, por que pone "shared", asi que igual es compartido por todos los modulos, pero en el dibujo no se ve, por que la L2 también es shared…

No se, la verdad es que si es curioso si...

-

Bueno, ya van saliendo cosillas:

http://www.anandtech.com/show/3863/amd-discloses-bobcat-bulldozer-architectures-at-hot-chips-2010

http://blogs.amd.com/work/Al final nada de CMT, que rabia, sin saber mucho más tienen pinta de ir a competir con nehalem y los Sandy Bridge de 4 núcleos, pero con los Sandy Bridge de 8 núcleos dificil.

-

La intención de AMD con bulldozer y estos módulos dual core es tener "dual cpus" cuyo rendimiento este entre SMT y CMP. La idea es ahorrar espacio, ya que según AMD , el segundo core en el modulo solo aumenta en 12% su área, de esta manera puede colocar mayor cantidad de estos modulos en un mismo chip. Si AMD logra colocar muchos mas de estos módulos que la cantidad de cores que intel pueda colocar en sus CPUs, creo que pueden tener alguna ventaja en aplicaciones que puedan dividirse en muchos threads. Ahora, la incógnita es aun el rendimiento single thread, parece que AMD ha mejorado el front-end tambien, haciendolo 4-issue. Ademas perece que han implementado un pre-fetching agresivo (similar al i7) y mejorado la unidad de prediccion de saltos. Esto, en teoría, debería representar una mejora en este aspecto; habrá que ver en la practica si realmente llega a alcanzar a los i7 clock for clock. Otra inquietud que me asalta es el rendimiento de aplicaciones multithreading que no tengan muchos threads, es decir, que solo usen 2 o 3. Habria que ver como sera la interaccion con el sistema operativo para que exista un verdadero rendimiento en estos casos CMP, y que no se compartan recursos en un mismo modulo, sobretodo si se están ejecutando instrucciones FP de 256 bits. Habra que ver como funciona esto también.

-

Bueno, ya van saliendo cosillas:

http://www.anandtech.com/show/3863/amd-discloses-bobcat-bulldozer-architectures-at-hot-chips-2010

http://blogs.amd.com/work/Al final nada de CMT, que rabia, sin saber mucho más tienen pinta de ir a competir con nehalem y los Sandy Bridge de 4 núcleos, pero con los Sandy Bridge de 8 núcleos dificil.

Si es cierto el hecho de que agregar el segundo core al modulo sin replicar las unidades FP solo aumenta el area un 12%, no veo porque AMD no pueda colocar 8 modulos en un chip, obteniendo asi 16 threads por chip. Ademas, según he leído Intel aun no ha anunciado CPUs de 8 cores. Teniendo en cuenta que un modulo de bulldozer potencialmente podria dar mas rendimiento que un core con SMT (ejecutando 2 threads simultaneos, por supuesto), creo que podria ser competitivo. Tambien habra que ver que mejoras hace intel a los sandy bridge, me parece que es mas un asunto de rendimiento por thread, que el numero de threads o de cores.

-

Si es cierto el hecho de que agregar el segundo core al modulo sin replicar las unidades FP solo aumenta el area un 12%, no veo porque AMD no pueda colocar 8 modulos en un chip, obteniendo asi 16 threads por chip. Ademas, según he leído Intel aun no ha anunciado CPUs de 8 cores. Teniendo en cuenta que un modulo de bulldozer potencialmente podria dar mas rendimiento que un core con SMT (ejecutando 2 threads simultaneos, por supuesto), creo que podria ser competitivo. Tambien habra que ver que mejoras hace intel a los sandy bridge, me parece que es mas un asunto de rendimiento por thread, que el numero de threads o de cores.

Hombre, poder puede sin problemas, el asunto es que en 32nm sea economicamente viable, por que además con 4 modulos tiene pinta de estar ya muy cerca de los 100w (AMD pone los bulldozer como de 10 a 100w en lo que a consumo se refiere).

Lo que comentas de amplicaciónes con pocos threads es algo que me pregunto yo también. Windows 7, a la hora de usar el SMT en los micros de Intel asigna los hilos en las CPU pares (cpu0, cpu2, cpu4…) para que no haya perdida de rendimiento y cuando llega al último los asigna a las unidades restantes, la solucion sería que en AMD ocurriera lo mismo. Viendo la numeración que pone AMD en los cores de cada modulo es hasta posible que pueda emplear el mismo sistema que Intel.

-

Pues al menos espero que sean competitvos, porque intel ya lleva mucho tiempo subido en la parra con los i7, a ver si bajan los precios y nos dejan a todos tener procesadores de ultima generacion.:D

-

Pues al menos espero que sean competitvos**, porque intel ya lleva mucho tiempo subido en la parra con los i7**, a ver si bajan los precios y nos dejan a todos tener procesadores de ultima generacion.:D

+1.

No puedo estar más de acuerdo.

-

Pues al menos espero que sean competitvos, porque intel ya lleva mucho tiempo subido en la parra con los i7, a ver si bajan los precios y nos dejan a todos tener procesadores de ultima generacion.:D

+1

Tienes toda la razón. A ver si AMD se pone las pilas y empieza a sacar procesadores que realmente sean competitivos y puedan dar más guerra con los de Intel, que a la postre beneficia al consumidor.

-

Pues mas rumores o no según se mire.

Según informa la web DonanimHaber.com, AMD dio a conocer algunas cifras de rendimiento de su próxima arquitectura en una presentación para sus socios. A tenor de lo adelantado por la compañía, un procesador de 8 núcleos basado en “Bulldozer” tendría un rendimiento un 50% mayor que los procesadores de gama alta existentes, como el Core i7 950 (4 núcleos, 8 hilos) y el Phenom II X6 1100T (6 núcleos), destacando sobretodo en juegos y aplicaciones de renderizado. No se han facilitado datos sobre la frecuencia del procesador ni el equipo donde fue testeado, pero si esas cifras son ciertas, lo dejarían incluso por encima del Core i7 980X de seis núcleos, el procesador de escritorio más rápido de Intel en estos momentos.

-

Y se sabe para cuando o una aproximación?

-

Pues se dice que para el 2 trimestre de este años, ya veremos.

-

-

Algunas novedades sobre los Bulldozer: El Turbo Core 2.0

AMD Turbo Core 2.0 es una versión evolucionada de la actual tecnología Turbo Core presente en los microprocesadores AMD Zosma y Thuban. Como se sabe, la actual tecnología Turbo Core eleva la frecuencia de funcionamiento de la mitad de los núcleos (2 a 3) de los CPUs AMD Phenom II X4 y X6, entre 400MHz (modelos cuyo nombre termina en 0T) a 500MHz (modelos cuyo nombre termina en 5T); la nueva tecnología Turbo Core 2.0 muestra una mayor flexibilidad pudiendo elevar la frecuencia de funcionamiento de todos los núcleos/módulos en los microprocesadores basados en la arquitectura Bulldozer, en concreto, todos los núcleos del microprocesador (hasta 16 de ellos) tendrán 500MHz adicionales (dependiendo del TDP) en situaciones de alta demanda de procesamiento y uso de todos los núcleos, mientras que en tareas que requieran pocos hilos de procesamiento se incrementará la frecuencia de la mitad de los núcleos en 600MHz o más (cifra aún no revelada por AMD pero que afirman será mayor a 500MHz).

http://tengotecno.com/wp-content/plugins/wp-o-matic/cache/347ac_turbocore2-1-590x352.jpg

Fuente: http://xtreview.com/addcomment-id-15425-view-amd-technology-turbo-core-2.0.html

-

Aunque el nombre no me gusta mucho, del resto me gusta todo;D No obstante, veremos el precio, porque la comparativa es con los opteron, no son muy baratos y pertenecen a la plataforma server, habría que comprararlos con los Xeon de intel. En cualquier caso, buenas noticias.